| Première version | |

|---|---|

| Dernière version | IEEE 1076-2019[1] |

| Type |

Langage de description de matériel Langage de modélisation |

| Site web | www.vhdl.org |

VHDL est un langage de description de matériel destiné à représenter le comportement ainsi que l'architecture d’un système électronique numérique. Son nom complet est VHSIC[2] Hardware Description Language.

L'intérêt d'une telle description réside dans son caractère exécutable : une spécification décrite en VHDL peut être vérifiée par simulation, avant que la conception détaillée ne soit terminée. En outre, les outils de conception assistée par ordinateur permettant de passer directement d'une description fonctionnelle en VHDL à un schéma en porte logique ont révolutionné les méthodes de conception des circuits numériques, ASIC ou FPGA.

Historique

Le langage VHDL a été commandé dans les années 1980 par le Département de la Défense des États-Unis dans le cadre de l'initiative VHSIC[3]. Dans un effort de rationalisation, le VHDL reprend la même syntaxe que celle utilisée par le langage Ada (ce dernier étant aussi développé par le département de la défense).

La version initiale de VHDL, standard IEEE 1076-1987, incluait un large éventail de types de données, numériques (entiers, réels), logiques (bits, booléens), caractères, temps, plus les tableaux de bits et chaînes de caractères.

L'un des principaux problèmes concernait le type bit. Celui-ci ne pouvant prendre que 2 valeurs (0, 1), il était impossible de représenter les signaux de valeur inconnue ou encore les signaux en haute impédance, ainsi que la « force » d'un signal (faible, forte ou nulle). La norme IEEE 1164 définit le type std_logic avec 9 états possibles. Ceci a été adopté dans le VHDL-93 (seconde version de la norme IEEE 1076).

Afin de répondre aux différents problèmes de l'électronique, la norme VHDL a dû évoluer. L'IEEE Design Automation Standards Committee (DASC) a créé la norme IEEE 1076.1 (1999), ou VHDL-AMS (VHDL-Analog and Mixed Systems).

Cette nouvelle norme est une extension de la norme IEEE 1076-1987 déjà existante. Elle permet la description et la simulation de circuits analogiques, numériques, et mixtes (analogique et numérique). Pour cela elle utilise en complément des instructions séquentielles et concurrentes un nouveau type d'instructions, dites « simultanées », et qui ont valeur d'équations. En pratique, de plus en plus de simulateurs implémentent cette extension. Par contre, les outils de synthèse analogique associés n'en sont encore qu'à leurs balbutiements[4].

Positionnement par rapport au Verilog

Le langage Verilog, bien que très différent du point de vue syntaxique, répondait à des besoins similaires. Il existe de fait une quasi-équivalence entre les deux langages, d'où l'existence de nombreux scripts de traduction de l'un vers l'autre. Le langage VHDL est maintenant le langage de description matérielle majoritairement utilisé par les entreprises européennes alors que Verilog est souvent préféré de l'autre côté de l'Atlantique.

Introduction au VHDL

Simulation et synthèse

Le but d'un langage de description matériel tel que le VHDL est de faciliter le développement d'un circuit numérique en fournissant une méthode rigoureuse de description du fonctionnement et de l'architecture du circuit désirée. L'idée est de ne pas avoir à réaliser (fondre) un composant réel, en utilisant à la place des outils de développement permettant de vérifier le fonctionnement attendu. Ce langage permet en effet d'utiliser des simulateurs, dont le rôle est de tester le fonctionnement décrit par le concepteur.

L'étape suivante consiste à synthétiser cette description matérielle pour obtenir un composant réalisant les fonctions désirées, à l'aide d'éléments logiques concrets (portes logiques, bascules ou registres). Ceux-ci seront implémentés, selon la technologie utilisée, soit directement en transistors (dans le cas d'un ASIC), ou en se basant sur les éléments programmables des FPGA. Après la synthèse viennent les phases de :

- placement : on choisit l'emplacement physique des différents éléments ;

- routage : on détermine les connexions entre éléments.

Ces deux opérations doivent prendre en compte les ressources disponibles sur l'ASIC (surface) ou dans le FPGA (unités programmables).

Le VHDL ayant une double fonction (simulation et synthèse), une partie seulement du VHDL est synthétisable, l'autre existant uniquement pour faciliter la simulation (écriture de modèles comportementaux et de test benches). Selon le support matériel et le logiciel de synthèse utilisés, cette partie pourra être plus ou moins étendue. De manière à obtenir du VHDL synthétisable et portable, il est donc nécessaire de se limiter à des constructions simples, dont la transcription en portes et bascules est simple à réaliser. La norme 1076.6 a été initiée pour tenter de définir un sous-ensemble de VHDL « de synthèse ».

Le langage

La syntaxe du VHDL est tirée du langage Ada, dont les mots clefs ont été adaptés à la conception matérielle. L'une des particularités du VHDL provient du fait qu'il est possible d'exprimer facilement le parallélisme présent à l'intérieur d'un circuit.

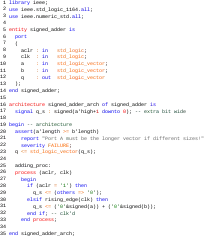

En VHDL, tout composant (dans le sens logiciel) est décrit sous deux aspects :

- L'interface avec le monde extérieur, décrite dans une section dénommée entity ;

- L'implémentation elle-même, décrite dans une section dénommée architecture.

C’est donc la section architecture qui contient la description de la fonction matérielle désirée :

- soit sous forme de description structurelle précise de l’architecture matérielle (les portes logiques à utiliser et leurs interconnexions) ;

- soit sous forme de comportement attendu, c'est-à-dire orienté fonctionnel.

Dans ce dernier cas, la description peut faire usage d'instructions concurrentes, utilisant principalement des affectations définitives (A <= B; qui se lit A reçoit B mais correspond à une connexion permanente du signal B vers le signal A) conditionnelles (A <= B when condition else C; qui signifie : A reçoit B si la condition est vraie, C sinon, mais toute modification de B, C ou de la condition a un effet immédiat) et sélective (with selecteur A <= B when valeur1, C when valeur2, D when others version concurrente du sélecteur switch-case du langage C). Comme leur nom l'indique, les instructions concurrentes simulent le parallélisme des circuits décrits. L'ordre des instructions concurrentes n'a aucun impact sur le circuit décrit.

Cependant, lorsqu'une fonction logique est trop complexe pour être décrite par une instruction concurrente, on peut lui substituer une description algorithmique appelée process. À l'intérieur de ces process, les instructions utilisées sont, cette fois-ci, séquentielles. Il s'agit des structures de contrôle classiques des langages de programmation (if-else, case-when, for/while) qui offrent la possibilité de mettre en œuvre n'importe quel algorithme, du moins en simulation.

Lors de la simulation, un process n'est exécuté que sur un déclenchement explicite, autrement il est inactif. Du point de vue matériel, un process est une « boîte noire » dont seul le comportement est décrit mais pas la structure. D'un point de vue logiciel un process se comporte comme une boucle infinie, dont chaque itération est déclenchée par une activité d'un de ses signaux d'entrée (inclus dans sa liste de sensibilité). Ainsi, les instructions for et while ne sont pas utiles pour décrire des compteurs, contrairement aux croyances habituelles des débutants en VHDL.

Deux difficultés

Double sens du mot « séquentiel »

Instruction « séquentielle » dans un process, s'oppose à instruction « concurrente » (hors d'un process) et non à combinatoire (pour la logique décrite), ce qui constitue une source de confusion très fréquente chez les débutants. En effet, on peut décrire un système combinatoire par un algorithme séquentiel (if A=1 then B <= C; else B<=0; end if; correspond à une porte ET) comme on peut décrire un circuit séquentiel par une instruction concurrente (Q <= Q when LE = '1' else D). Seuls les circuits séquentiels synchrones (sensibles aux fronts du signal d'horloge) ne peuvent être décrits qu'avec un algorithme activé sur le front de l'horloge.

Un signal n'est pas une variable

Dans un process, on peut trouver des affectations de signaux ou de variables. Contrairement aux variables, l'affectation du signal n'a pas un effet immédiat. On ne peut modifier que la valeur future du signal. Par défaut, c'est la valeur que prendra ce signal au prochain pas de simulation qui est affectée, valeur qui ne deviendra effective qu'après la fin du process. Ainsi, dans un process, après cinq instructions A <= A+1;, le signal A n'est pas augmenté de 5 mais seulement de 1. Il faut lire A.futur <= A.présent +1; de sorte que A.présent n'est jamais modifié.

Différences avec un langage de programmation

Le VHDL a deux aspects qui peuvent être contradictoires. Lorsqu'il s'agit d'écrire un modèle comportemental qui sera simplement simulé, le langage est compilé puis exécuté par le simulateur. Par contre lorsqu'il s'agit de décrire un circuit qui sera créé par un synthétiseur, la philosophie est sensiblement différente. L'outil de synthèse, devant transformer l'ensemble du code fourni en une implémentation à base de portes logiques, est conçu pour fonctionner de manière très cadrée. Il est nécessaire de pouvoir lui fournir une description claire (dont la synthèse correspond à l'architecture recherchée) tout en étant le moins spécifique possible (afin de permettre à l'outil d'optimiser au maximum le circuit généré).

Par exemple, si l'on désire générer une fonction de logique combinatoire (indépendante de toute horloge), il faudra affecter l'ensemble des sorties à chaque appel du process, sans quoi l'outil de synthèse, considérant que les sorties non assignées conservent leur ancienne valeur, placera des bascules D en sortie de chaque sortie non affectée. Cette solution est alors très mauvaise, puisqu'elle transforme la fonction en une fonction de logique synchrone, donc dépendant d'une horloge (qui de plus est spécifiée par l'outil de synthèse, hors de contrôle du concepteur).

Cette différence implique un grand travail en amont et en aval du codage, le circuit décrit doit avoir déjà été pensé avant d'être codé et il doit être vérifié après conception, en considérant le nombre de portes et les caractéristiques d'implantation, afin de s'assurer qu'aucune erreur de description n'est présente. Ces contraintes très fortes sur le programmeur entrainent l'adoption de guides de conduites et de méthodes de codage très strictes.

Ces grandes différences avec un langage de programmation comme le C font du VHDL un langage à part, plus proche de l'électronique que de l'informatique. Il n'est d'ailleurs pas rare de voir implémenté sur des FPGA des architectures de micro-contrôleurs, eux-mêmes programmés en assembleur ou en C dans la suite du projet.

Logiciels pour débuter en VHDL

Environnement de développement intégré

Les principaux fabricants de circuits logiques programmables proposent une version gratuite mais limitée de leurs outils.

| Éditeur | Produit | Licence | Synthétiseur | Simulateur | Remarques |

|---|---|---|---|---|---|

| Xilinx | ISE Webpack[5] | Propriétaire, gratuite, illimité | Oui | Oui | Simulateur ModelSim XE Starter gratuit |

| Altera | Quartus II Web Edition[6] | Propriétaire, gratuite, 6 mois renouvelable | Oui | Oui | Simulateur ModelSim Altera Starter Edition gratuit |

| Lattice | ispLever starter[7] | Propriétaire, gratuite, 6 mois renouvelable | Oui | Oui | Synthétiseur : Synplify Pro for Lattice (gratuit), Simulateur Active-HDL Lattice edition (gratuit) |

| Actel | Libero[8] | Propriétaire, gratuite, 1 an renouvelable | Oui | Oui | Synthétiseur : Synplify Pro Actel Edition (gratuit), Simulateur ModelSim Actel Edition (gratuit) |

| Simulateurs uniquement | |||||

| Aldec | Active-HDL Student Edition[9] | Propriétaire, gratuite, 1 an | Tiers partie | Oui | |

| Mentor Graphics | ModelSim PE Student Edition[10] | Propriétaire, gratuite | Non | Oui | |

| Dolphin Integration | SMASH[11] | Propriétaire, gratuite | Non | Oui | Simulateur SMASH Discovery gratuit (avec exemples en VHDL) |

Éditeur de texte

Les environnements de développement mentionnés précédemment permettent tous la saisie d'un fichier VHDL, toutefois certains éditeurs de texte proposent des fonctionnalités avancées comme la coloration syntaxique, le complètement automatique, le pliage de code ou encore des macro-commandes. C'est le cas des logiciels libres suivants :

- Emacs

- Notepad++

- Crimson Editor (mode colonne très performant)

- Vim

- Smultron (Mac OSX)

- Scite

- gedit (Unix)

- kwrite (Unix)

- Visual Studio Code (avec extension)

Exemples de descriptions en VHDL

Hello World

Certains concepts, comme les fichiers ou l'échelle de temps, n'ont de sens que pour la modélisation d'un composant électronique et ne sont pas accessibles au composant lui-même. L'affichage d'une chaîne de caractères sur la sortie standard étant également un concept abstrait, elle n'est possible qu'en simulation.

-- Déclaration de l'entité

entity hello_world is

end entity hello_world;

-- Déclaration de l'architecture

architecture wiki of hello_world is

begin

-- Process affiche_texte

affiche_texte: process is

begin

-- Afficher la chaine de caractère "Hello world !" sur la sortie standard du simulateur

report "Hello world !";

-- Suspendre l'exécution du process

wait;

end process affiche_texte;

end architecture wiki;

Clignotant

Il existe plusieurs descriptions possibles d'un composant dont l'une des sorties change d'état après un temps déterminé.

--------------------------------------------------------------------------------

-- Liste des librairies et objets importés

library ieee;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

--------------------------------------------------------------------------------

-- Déclaration de l'entité

entity Clignotant is

-- Paramètres passés lors de la génération (compilation ou synthèse)

generic (

PERIODE : integer := 100000000;

DUREE_ETAT_BAS : integer := 75000000

);

-- Entrées / sorties

port (

CLK : in std_logic;

RESET : in std_logic;

LED : out std_logic

);

end entity Clignotant;

--------------------------------------------------------------------------------

architecture RTL of Clignotant is

-- Déclaration des signaux utilisés dans l'implémentation

signal Compteur_s : unsigned(31 downto 0);

begin

-- Process synchrone "Compteur"

Compteur: process(CLK)

begin

if rising_edge(CLK) then

-- La suite est exécutée après chaque front montant de l'entrée CLK

if (RESET = '1') then

-- Reset actif à l'état haut

Compteur_s <= (others => '0');

LED <= '0';

else

if (Compteur_s < DUREE_ETAT_BAS) then

-- Maintenir la LED éteinte

LED <= '0';

else

-- Allumer la LED

LED <= '1';

end if;

if (Compteur_s >= PERIODE) then

-- Recommencer un cycle

Compteur_s <= (others => '0');

else

-- Continuer le cycle

Compteur_s <= Compteur_s + 1;

end if;

end if;

end if;

end process Compteur;

-- Fin du process "Compteur"

end architecture RTL;

-- Fin du fichier

Un multiplexeur 4 vers 1 (trois architectures concurrentes différentes)

En VHDL, il faut distinguer le contenant du contenu, nommés respectivement entité et architecture.

Le fichier VHDL

Un fichier VHDL doit toujours porter le nom de l'entité qu'il contient (ceci est une règle d'utilisation qui aide à la clarté, elle est même obligatoire avec certains logiciels). Son extension standard est « .vhd », bien que l'on écrive parfois « .vhdl ». Avant toute chose, il faut commencer par déclarer l'utilisation des bibliothèques nécessaires au projet :

-- En VHDL : une ligne de commentaires commence avec deux "-"

-- Il est préférable de commencer par importer les bibliothèques VHDL standards normalisées par l'IEEE,

-- car elles sont souvent nécessaires.

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

Les bibliothèques std_logic_arith, std_logic_signed et std_logic_unsigned, malgré leur nom, ne sont pas normalisées par l'IEEE et leur utilisation est fortement déconseillée. En effet, il est préférable de préciser explicitement le type de chaque vecteur sur lequel on fait une opération (SIGNED ou UNSIGNED) de manière à spécifier son traitement arithmétique. Le comportement des opérations sur les types STD_LOGIC_VECTOR sera différent selon la bibliothèque appelée, ce qui rend leur utilisation hasardeuse.

L'entité

Description de l'interface (l'entité) d'un multiplexeur à quatre entrées :

-- Voici un exemple d’entité, décrivant les E/S utilisées

-- par les trois exemples d’architectures purement concurrentes :

--

-- ATTENTION, avec certains outils de CAO, l'entité doit avoir le même nom que le fichier (logique_4_vers_1.vhd)

ENTITY logique_4_vers_1 IS

PORT

(

a : IN STD_LOGIC;

b : IN STD_LOGIC;

c : IN STD_LOGIC;

d : IN STD_LOGIC;

adr : IN STD_LOGIC_VECTOR (1 downto 0);

s : OUT STD_LOGIC

);

END logique_4_vers_1;

Première Architecture

La première architecture permettant de décrire ce multiplexeur utilise directement une formulation booléenne, utilisable en pratique seulement pour des équations simples. Cette méthode permet d'écrire toute fonction combinatoire.

-- Première architecture concurrente décrivant un mux :

ARCHITECTURE mux_4_vers_1 OF logique_4_vers_1 IS

BEGIN

s <= ( a AND NOT adr(1) AND NOT adr(0) )

OR ( b AND NOT adr(1) AND adr(0) )

OR ( c AND adr(1) AND NOT adr(0) )

OR ( d AND adr(1) AND adr(0) );

END mux_4_vers_1;

Deuxième Architecture

La deuxième architecture utilise les mots clés WITH, SELECT et WHEN. Le comportement en simulation d'une telle écriture peut être différent de la première lorsque les entrées ont pour valeur X ou Z.

-- Deuxième architecture concurrente décrivant un mux :

ARCHITECTURE mux_4_vers_1 OF logique_4_vers_1 IS

BEGIN

WITH adr SELECT

s <= a WHEN "00",

b WHEN "01",

c WHEN "10",

d WHEN others;

END mux_4_vers_1;

La dernière ligne permet de regrouper tous les cas non explicitement traités en une seule ligne.

Troisième architecture

La troisième architecture utilise les mots clés WHEN et ELSE.

-- Troisième architecture concurrente décrivant un mux :

ARCHITECTURE mux_4_vers_1 OF logique_4_vers_1 IS

BEGIN

s <= a WHEN adr = "00" ELSE

b WHEN adr = "01" ELSE

c WHEN adr = "10" ELSE

d;

END mux_4_vers_1;

Architecture séquentielle - une bascule D

La description d'une architecture séquentielle, c’est-à-dire avec l'aide d'une fonction dépendante du temps (ie. de l'horloge) passe par l'utilisation de process.

-- Architecture séquentielle pour une bascule D :

ARCHITECTURE comport OF bascule_d IS

BEGIN

PROCESS (clk, reset)

BEGIN

IF reset = '1' THEN

q <= '0';

ELSE

IF clk'event AND clk = '1' THEN -- Moins bien que : IF rising_edge(clk) THEN

q <= d;

END IF;

END IF;

END process;

END comport;

Notes

- ↑ « https://ieeexplore.ieee.org/document/8938196 »

- ↑ VHSIC signifie Very High Speed Integrated Circuit.

- ↑ (en) Peeter Ellervee, Kalle Tammemäe VHDL - VHSIC Hardware Description Language[PDF], Tallinn University of Technology - Department of Computer Engineering, visité le 24 septembre 2008

- ↑ http://www.univ-bpclermont.fr/FORMATIONS/Master/meam/cme/cme02.pdf [PDF] p. 30-47

- ↑ Xilinx : ISE WebPACK

- ↑ Quartus II Web Edition Software Version 7.2

- ↑ ispLEVER Starter

- ↑ Libero

- ↑ Students - Active-HDL Student Edition

- ↑ ModelSim - Technical Resources: ModelSim PE Student Edition Overview

- ↑ SMASH

Voir aussi

Articles connexes

- langage de description de matériel

- VHDL-AMS

- Verilog

- Verilog-AMS

- SystemC

- Boundary scan description language (BSDL)