Le PCI Express (Peripheral Component Interconnect Express), officiellement abrégé PCI-E ou PCIe est un standard de bus d'extension[1] utilisé pour les échanges entre les cartes d'extension (cartes graphiques, SSD, disques durs, cartes réseau,…) et avec la carte mère d'un ordinateur. Développé par Intel et introduit en 2004, il supplante les standards antérieurs PCI, PCI-X et AGP.

Par analogie avec le modèle OSI, le standard PCI Express spécifie une couche physique, dont un bus local, couramment appelé (« bus PCI express »), une couche liaison de données et une couche de transaction.

Le PCI-SIG (Special Interest Group) est le groupe de travail, représentant plus de huit cent sociétés, qui s'occupe du maintien et du développement du standard PCI Express[2]. La dernière version du standard est la spécification PCI Express 6.0, offrant un débit de 64 GT/s par canal, publiée le 11 janvier 2022[3]. La version 7.0 du protocole est à l'étude. PCI Express est une marque déposée.

Une évolution du PCI

Un avantage du PCI Express est d’être dérivé de la norme PCI (Peripheral Component Interconnect), ce qui permet aux constructeurs d’adapter simplement leurs cartes d’extension existantes, puisque seule la couche matérielle est à modifier. D’autre part, il est suffisamment rapide pour pouvoir remplacer non seulement le PCI classique mais aussi l’AGP, un port rapide pour cartes graphiques.

Contrairement au PCI qui est relié au southbridge de la carte mère, le PCI Express est souvent disponible à la fois au niveau du northbridge et du southbridge, il a même été intégré en à certains microprocesseurs.

Alors que le PCI utilise un unique bus de largeur 32 bits bidirectionnel alterné (half duplex) pour l’ensemble des périphériques, le PCI Express utilise une interface série (de largeur 1 bit) à base de lignes bidirectionnelles réparties sur 8 broches. On pourra ainsi parler d’une carte mère possédant 20 lignes PCIe. Une ligne permet théoriquement des échanges full duplex à 250 Mo/s pour la version 1.1 du protocole. Les différents périphériques communiquent alors par échange de paquets et l’arbitrage du bus PCI est remplacé par un commutateur. Le principe de fonctionnement est semblable à de la commutation de paquets selon un modèle à quatre couches :

- couche logicielle : codage/décodage des paquets de données ;

- couche transaction : rajout/suppression d’un en-tête de début et d’un en-tête de séquencement ou de numérotation du paquet ;

- couche liaison : rajout/suppression d’un code de correction d’erreur (contrôle de redondance cyclique) ;

- couche physique : transmission du paquet (transmission série « point à point »).

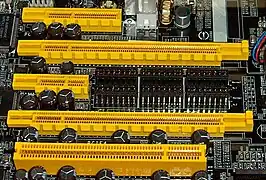

On parle de ports PCIe ×1, ×2, ×4, ×8, ×16 et ×32 pour différencier les ports en fonction du nombre de connecteurs de ligne dont ils disposent (respectivement 1, 2, 4, 8, 16 ou 32 lignes maximum). Un port ×32 permet d'atteindre en théorie un débit de 8 Go/s, soit quatre fois le débit des ports AGP[4].

Un port ×16 par exemple peut n’être relié qu’à huit lignes PCIe ; il devra tout de même avoir un apport de puissance électrique nécessaire aux cartes ×16[5]. Une carte d’extension ×16 fonctionnera sur ce port (mais probablement avec des performances non optimales), car le protocole PCIe prévoit la négociation mutuelle du nombre de lignes maximum supportées par les deux entités en relation. De même, une carte (exemple : ×1) peut être connectée et fonctionnera correctement sur un port plus grand (exemple : ×2, …, ×32).

Évolutions

Les évolutions du PCI Express ont été motivées principalement par le besoin d'augmenter le taux de transfert, qui est quasiment doublé à chaque nouvelle génération du standard par rapport à la génération précédente. De plus, chaque nouvelle génération est susceptible d'apporter d'autres avantages, qui sont décrits ci-dessous.

En 2007 est apparue la deuxième génération de PCIe (gen 2.0) qui permet, entre autres, de passer le débit de 250 à 500 Mo/s par sens par lien (le débit de la première génération gen 1.0 est doublé). En février de cette même année est publiée la norme « External PCI Express 1.0 » (ePCIe 1.0, Cabled PCIe 1.0)[6],[7], qui permet de connecter des périphériques externes sur le bus PCIe, en utilisant une carte permettant de rediriger celui-ci vers un connecteur externe. Le débit de chaque ligne est limité à 250 Mo/s. Il existe des connecteurs et des câbles pour les versions 1x, 4x, 8x et 16x du bus. Une évolution vers des lignes à 500 Mo/s (comme le PCIe 2.0) est prévue mais sans date annoncée.

En 2010, PCI-SIG publie le cahier des charges du PCIe (gen 3.0), originellement appelé 3GIO, 3rd Generation Input/Output, dont le débit est doublé 1 000 Mo/s grâce à une augmentation de 60 % de la fréquence qui passe à 5 à 8 GHz pour la gen 2.0, mais aussi par un codage 128 bits/130 bits. Au lieu de consommer 20 % du débit pour gen 2.0, ce codage ne fait plus perdre que 1,6 % de la bande passante totale. Les premiers périphériques en PCIe 3.0 sont arrivés mi-2011, mais les cartes graphiques exploitant cette interface ne sont arrivées que début 2012.

La spécification PCIe 4.0 est parue en . Elle double la bande passante. La première carte graphique à utiliser pleinement cette nouvelle spécification est la carte AMD Radeon RX 5700 XT en 2019[8],[9].

La spécification PCIe 5.0 est parue en avec un nouveau doublement de la bande passante[10]. Phison (en) a averti qu'avec les débits possibles avec la norme PCIe 5, les SSD les plus performants devraient adopter un système de refroidissement actif pour leur intégrité[11].

La spécification PCIe 6.0 est parue en avec un nouveau doublement de la bande passante[12].

| Version | Année de lancement | Codage | Taux de transfert par ligne[alpha 1] | Bande passante | |||||

|---|---|---|---|---|---|---|---|---|---|

| x1 | x2 | x4 | x8 | x16 | |||||

| 1.0 / 1.1 | 2003 | NRZ | 8b/10b | 2,5 GT/s | 250 Mo/s | 500 Mo/s | 1 Go/s | 2 Go/s | 4 Go/s |

| 2.0 | 2007 | 5 GT/s | 500 Mo/s | 1 Go/s | 2 Go/s | 4 Go/s | 8 Go/s | ||

| 3.0 | 2010 | 128b/130b | 8 GT/s | 985 Mo/s | 1,969 Go/s | 3,938 Go/s | 7,877 Go/s | 15,754 Go/s | |

| 4.0 | 2017 | 16 GT/s | 1,969 Go/s | 3,938 Go/s | 7,877 Go/s | 15,754 Go/s | 31,508 Go/s | ||

| 5.0 | 2019 | 32 GT/s | 3,938 Go/s | 7,877 Go/s | 15,754 Go/s | 31,508 Go/s | 63.015 Go/s | ||

| 6.0 | 2022 | PAM4 | 242b/256b

FLIT |

64 GT/s (32 GBd) | 7,563 Go/s | 15,125 Go/s | 30,25 Go/s | 60,5 Go/s | 121 Go/s |

| 7.0 | 2025 (prévu) | 128 GT/s (64 GBd) | 15,125 Go/s | 30,25 Go/s | 60,5 Go/s | 121 Go/s | 242 Go/s | ||

Spécifications techniques

Compatibilité emplacements/cartes

Les connecteurs PCI Express permettent la connexion d'une carte x8 (8 lignes) sur un emplacement x16 (16 lignes), l’inverse n'étant pas vrai, du fait de la différence de longueur des connecteurs ; idem pour les autres variantes. La taille du connecteur limite le nombre maximum de lignes PCIe utilisables par la carte, mais ne le garantit pas. La taille d'un connecteur sur une carte mère spécifie la vitesse qu'une carte ne pourra pas dépasser, compte tenu du nombre de lignes effectivement câblées, mais ne garantit pas que la carte qu'on y insère utilisera la totalité de ces lignes et donc fonctionnera effectivement à cette vitesse maximale. Pour assurer une rétro-comptabilité, le nombre de lignes utilisées, ainsi que la vitesse maximale par ligne, se négocie automatiquement entre les périphériques.

- Un périphérique x1 (ligne unique) dans un emplacement x16 fonctionnera logiquement en mode x1 ; cette configuration ne présente aucun inconvénient, sauf celui d'occuper un emplacement x16 qu'on aurait peut-être préféré utiliser avec un autre périphérique.

- Un périphérique x16 (16 lignes de communication) sera toujours capable de fonctionner en mode x1 (mais sera bridé par ce mode de fonctionnement) ; cet exemple est théorique, car dans la pratique il n'est pas envisageable d'insérer une carte x16 dans un connecteur x1, du fait de leurs longueurs différentes (sauf à « bidouiller » en retirant de la matière à l'extrémité du connecteur).

- Un périphérique Gen3 x4 dans un emplacement Gen2 x8 fonctionnera sur 4 lignes seulement (il n'en possède pas plus); par ailleurs, il ne pourra pas négocier un débit supérieur à celui autorisé par le bus Gen2 ; il sera donc accessible à la moitié de son débit théorique.

- Un périphérique Gen2 x8 dans un emplacement Gen3 x4 souffrirait de la même limitation ; là encore, le nombre de lignes et la vitesse maximale par ligne se négocieront sur le plus petit commun dénominateur entre le périphérique et le slot PCIe.

Pour un périphérique x16 dans un emplacement « physiquement » x16, son mode de fonctionnement pourra encore dépendre du câblage électrique de la carte mère, du nombre de cartes x16 utilisées ainsi que du modèle de processeur, de sa fréquence et du chipset (processeur de communication) utilisé. La présence d'autres cartes PCIe sur le bus pourra suivant les cas limiter le nombre de lignes effectivement utilisables sur cet emplacement en mode x16[13].

Dimensions

| Type PCI | Dimensions (mm) |

| Full-Length PCI Card | 106,68 mm (hauteur) X 312 mm (longueur) |

| Half-Length PCI Card | 106,68 mm (hauteur) X 175,26 mm (longueur) |

| Low-Profile/ Slim PCI Card | 64,41 mm (hauteur) X de 119,91 mm à 167,64 mm (longueur) |

| Lignes | Nombre de broches | Longueur | ||

|---|---|---|---|---|

| Total | Variable | Total | Variable | |

| ×1 | 2×18 = 36[14] | 2×7 = 14 | 25 mm | 7,65 mm |

| ×4 | 2×32 = 64 | 2×21 = 42 | 39 mm | 21,65 mm |

| ×8 | 2×49 = 98 | 2×38 = 76 | 56 mm | 38,65 mm |

| ×16 | 2×82 = 164 | 2×71 = 142 | 89 mm | 71,65 mm |

Brochage

Le tableau suivant indique les conducteurs de chaque côté du connecteur d'une carte PCI Express :

- le côté soudure du circuit imprimé (PCB) de la carte est le côté A, et le côté « composants » est le côté B ;

- les broches PRSNT1 # et PRSNT2 # doivent être légèrement plus courtes que les autres, pour s'assurer qu'une carte branchée à chaud est complètement insérée ;

- la broche WAKE # est utilisée pour indiquer que la carte est capable de se réveiller de façon autonome.

| Broche | Côté B | Côté A | Description | Broche | Côté B | Côté A | Description | |

|---|---|---|---|---|---|---|---|---|

| 1 | +12 V | PRSNT1# | Doit se connecter à la broche PRSNT2# la plus éloignée | 50 | HSOp(8) | Reserved | Voie 8 envoi des données, + et − | |

| 2 | +12 V | +12 V | Broches d'alimentation principale | 51 | HSOn(8) | Ground | ||

| 3 | +12 V | +12 V | 52 | Ground | HSIp(8) | Voie 8 réception des données, + et − | ||

| 4 | Ground | Ground | 53 | Ground | HSIn(8) | |||

| 5 | SMCLK | TCK | broches pour les ports SMBus et JTAG | 54 | HSOp(9) | Ground | Voie 9 envoi des données, + et − | |

| 6 | SMDAT | TDI | 55 | HSOn(9) | Ground | |||

| 7 | Ground | TDO | 56 | Ground | HSIp(9) | Voie 9 réception des données, + et − | ||

| 8 | +3.3 V | TMS | 57 | Ground | HSIn(9) | |||

| 9 | TRST# | +3,3 V | 58 | HSOp(10) | Ground | Voie 10 envoi des données, + et − | ||

| 10 | +3.3 V aux | +3.3 V | Alimentation de veille | 59 | HSOn(10) | Ground | ||

| 11 | WAKE# | PERST# | Lien de réactivation; fondamental pour le reset | 60 | Ground | HSIp(10) | Voie 10 réception des données, + et − | |

| Encoche | 61 | Ground | HSIn(10) | |||||

| 12 | CLKREQ# | Ground | Demande d'horloge de fonctionnement | 62 | HSOp(11) | Ground | Voie 11 envoi des données, + et − | |

| 13 | Ground | REFCLK+ | Paire différentielle d'horloge de référence | 63 | HSOn(11) | Ground | ||

| 14 | HSOp(0) | REFCLK− | Voie 0 envoi des données, + et − | 64 | Ground | HSIp(11) | Voie 11 réception des données, + et − | |

| 15 | HSOn(0) | Ground | 65 | Ground | HSIn(11) | |||

| 16 | Ground | HSIp(0) | Voie 0 réception des données, + et − | 66 | HSOp(12) | Ground | Voie 12 envoi des données, + et − | |

| 17 | PRSNT2# | HSIn(0) | 67 | HSOn(12) | Ground | |||

| 18 | Ground | Ground | 68 | Ground | HSIp(12) | Voie 12 réception des données, + et − | ||

| Les cartes PCI Express ×1 se terminent à la broche 18 | 69 | Ground | HSIn(12) | |||||

| 19 | HSOp(1) | Reserved | Voie 1 envoi des données, + et − | 70 | HSOp(13) | Ground | Voie 13 envoi des données, + et − | |

| 20 | HSOn(1) | Ground | 71 | HSOn(13) | Ground | |||

| 21 | Ground | HSIp(1) | Voie 1 réception des données, + et − | 72 | Ground | HSIp(13) | Voie 13 réception des données, + et − | |

| 22 | Ground | HSIn(1) | 73 | Ground | HSIn(13) | |||

| 23 | HSOp(2) | Ground | Voie 2 envoi des données, + et − | 74 | HSOp(14) | Ground | Voie 14 envoi des données, + et − | |

| 24 | HSOn(2) | Ground | 75 | HSOn(14) | Ground | |||

| 25 | Ground | HSIp(2) | Voie 2 réception des données, + et − | 76 | Ground | HSIp(14) | Voie 14 réception des données, + et − | |

| 26 | Ground | HSIn(2) | 77 | Ground | HSIn(14) | |||

| 27 | HSOp(3) | Ground | Voie 3 envoi des données, + et − | 78 | HSOp(15) | Ground | Voie 15 envoi des données, + et − | |

| 28 | HSOn(3) | Ground | 79 | HSOn(15) | Ground | |||

| 29 | Ground | HSIp(3) | Voie 3 réception des données, + et − | 80 | Ground | HSIp(15) | Voie 15 réception des données, + et − | |

| 30 | Reserved | HSIn(3) | 81 | PRSNT2# | HSIn(15) | |||

| 31 | PRSNT2# | Ground | 82 | Reserved | Ground | |||

| 32 | Ground | Reserved | ||||||

| Les cartes PCI Express ×4 se terminent à la broche 32 | ||||||||

| 33 | HSOp(4) | Reserved | Voie 4 envoi des données, + et − | |||||

| 34 | HSOn(4) | Ground | ||||||

| 35 | Ground | HSIp(4) | Voie 4 réception des données, + et − | |||||

| 36 | Ground | HSIn(4) | ||||||

| 37 | HSOp(5) | Ground | Voie 5 envoi des données, + et − | |||||

| 38 | HSOn(5) | Ground | ||||||

| 39 | Ground | HSIp(5) | Voie 5 réception des données, + et − | |||||

| 40 | Ground | HSIn(5) | ||||||

| 41 | HSOp(6) | Ground | Voie 6 envoi des données, + et − | |||||

| 42 | HSOn(6) | Ground | ||||||

| 43 | Ground | HSIp(6) | Voie 6 réception des données, + et − | Legendes | ||||

| 44 | Ground | HSIn(6) | Ground pin | Référence de zéro volt | ||||

| 45 | HSOp(7) | Ground | Voie 7 envoi des données, + et − | Power pin | Alimentation de la carte PCIe | |||

| 46 | HSOn(7) | Ground | Output pin | Signal de la carte fille à la carte mère | ||||

| 47 | Ground | HSIp(7) | Voie 7 réception des données, + et − | Input pin | Signal de la carte mère à la carte fille | |||

| 48 | PRSNT2# | HSIn(7) | Open drain | Peut être mis à un niveau bas ou détecté par de multiples cartes | ||||

| 49 | Ground | Ground | Sense pin | Reliées ensemble sur la carte pour permettre la détection du type de carte | ||||

| Les cartes PCI Express ×8 se terminent à la broche 49 | Reserved | Pas utilisé actuellement, ne pas connecter | ||||||

Caractéristiques

Deux liens différentiels permettent l'échange de données en émission (direct) et réception (revers) entre deux points A & B.

'n' de ces liens constituent alors les chemins d'échange (lane) : PCIe 1x 2x 4x 8x.

Un signal émission ou réception est donc composé de deux fils en mode différentiel.

La combinaison des signaux émission et réception, soit 4 fils, constitue un chemin (lane).

Le regroupement de 'n' chemins représente le lien PCIe nX.

Un composant Root permet l'accès au CPU, à la mémoire ou tout autre périphérique.

Un composant Switch (optionnel) permet le transfert PCIe entre end point sans passer par le Root.

Les End point sont les périphériques d'échange.

Les données sont élaborées sous forme de paquets.

PCIe permet le contrôle de flux, la QoS, la virtualisation de canaux, une latence prévisible...

Débit et bande passante :

Une paire différentielle permet un débit de 2,5 Gbit/s

PCIe 1x aura donc un débit utile de (2,5 * 1000 * 2 * 8/10)/8 = 500 Mo/s

Le facteur 2 vient du mode full duplex émission + réception.

Le facteur 8/10 est introduit par le codage 8b/10b utilisé.

PCIe suit le modèle OSI :

- la couche PHYsique permet le passage des paquets en un flux série (PCS/PMA layer) ;

- la couche Data link permet la gestion de l'intégrité du lien (LCRC) et le contrôle de flux ;

- la couche Transaction permet les accès plus haut niveau : mémoire, I/O...

Un calcul de CRC est effectué au niveau data link, il permet de vérifier l'intégrité des échanges à ce niveau. Un deuxième calcul est réalisé au niveau transactionnel, c'est un calcul de CRC de bout en bout (ECRC).

Si l'ECRC est faux, il est possible de demander de renvoyer à nouveau le paquet.

Ceci est géré au niveau data link par un paquet DLLP (data link layer paquet) spécifique.

Les paquets de type DLLP sont transparents à l'utilisateur qui ne voit que les paquets TLP en général.

Les DLLP sont donc des paquets de management (completion, configuration).

Software layer *data* +-------------------+ | Transaction layer | **Header,*data*,ecrc** +-------------------+ | Data Link Layer | | | ***Sequence,**Header,*data*,ecrc**,lcrc*** +-------------------+ | PHYsical Layer | | | Start,***Sequence,**Header,*data*,ecrc**,lcrc***,End +-------------------+

L'en tête du packet PCIe est de 3 à 4 mots de 32 bits.

La zone de charge utile, data, est de 0 à 1024 mots de 32 bits.

Un mot de 32 bits est appelé Double Word (DW) sachant qu'un word est un double octet et qu'un octet est composé de 8 bits.

Le niveau physique est composé des éléments suivants :

- circuit de récupération d'horloge (côté réception), (PMA) ;

- SerDes (en), (PMA) ;

- embrouilleur, (PMA) ;

- codage 8b/10b (PCS).

Le niveau data link dispose d'un "Replay Buffer" côté émission permettant de renvoyer le paquet lorsque le récepteur détecte des erreurs.

Différents types de transactions existent :

- lecture ou écriture du plan mémoire ;

- configuration en phase d'initialisation ;

- messages permettant l'échange d'événements entre périphériques ;

- achèvement (completion) de la transaction.

Deux types de transactions sont possibles : postée ou non postée.

La transaction de type postée envoie un paquet et n'attend rien en retour : c'est comme une lettre à la poste.

La transaction de type non postée qui attend un paquet d'achèvement en retour : c'est comme une lettre en recommandée.

Une écriture mémoire sera de type posté alors qu'une lecture mémoire sera de type non posté.

Si l'usage fait de PCIe est simple, l'utilisateur peut se brancher au niveau transactionnel.

Il faudra alors gérer les paquets TLP (transaction layer paquet) en émission réception.

Pour des usages plus poussés, des IP existent (cas d'un design FPGA).

Cette surcouche gérera par exemple des accès mémoire direct DMA en mode "scatter gather" éventuellement.

Notes et références

Notes

- ↑ Par paire différentielle et dans chaque direction (canaux simplex bi-directionnels).

Références

- ↑ Definition PCIe, lemagit.fr, consulté le 28 novembre 2022.

- ↑ « Membership | PCI-SIG », sur pcisig.com (consulté le )

- ↑ pascal Meyrou, « Le cap'tain PCI-SIG sort le foc : cap sur le PCI Express 7.0 », sur comptoir du hardware,

- ↑ Bus PCI Express (PCI-E), sur Comment ça marche (consulté le 16 février 2016).

- ↑ « Puissance supplémentaire requise par certaines cartes graphiques PCI Express * pour carte Cartes mères Intel® pour PC de bureau »

, sur intel.fr (consulté le )

, sur intel.fr (consulté le ) - ↑ (en) « Spécification PCI Express External Cabling 1.0 » (consulté le )

- ↑ (en) « Spécification mise à jour du PCI Express External Cabling 1.0 », Pci-Sig, (consulté le )

- ↑ (en) PCI-Express 4.0 Performance Scaling with Radeon RX 5700 XT, techpowerup.com, (consulté le 28 novembre 2022).

- ↑ PCI Express 4.0 : la version 1.0 maintenant officiellement publiée, sur Tom's Hardware, 26 octobre 2017 (consulté le 17 janvier 2018).

- ↑ (en) « PCI-SIG® Achieves 32GT/s with New PCI Express® 5.0 Specification » (consulté le )

- ↑ « Bientôt, les SSD ne pourront plus se passer d'un refroidissement actif », sur Clubic, .

- ↑ (en) « PCI-SIG® Releases PCIe® 6.0 Specification Delivering Record Performance to Power Big Data Applications », sur www.businesswire.com, (consulté le )

- ↑ PCIe : le PCI express expliqué en quelques lignes, sur tomshardware.fr du 3 décembre 2014, consulté le 3 février 2017

- ↑ « PCI Express 1x, 4x, 8x, 16x bus pinout and wiring @ » [archive du ], RU, Pinouts (consulté le )

Voir aussi

Articles connexes

- Peripheral Component Interconnect (PCI)

- HyperTransport

- InfiniBand

- Accelerated Graphics Port (AGP)

- Gen-Z

Sources

- Andrew Tanenbaum, L'Architecture des ordinateurs, éd. Pearson