Les architectures ARM sont des architectures externes de type RISC 32 bits (ARMv1 à ARMv7) et 64 bits (ARMv8)[1] développées par ARM Ltd depuis 1983 et introduites à partir de 1990 par Acorn Computers. L'architecture ARM est le fruit du travail de Sophie Wilson.

Dotés d'une architecture relativement plus simple que d'autres familles de processeurs et faibles consommateurs d'électricité, les processeurs ARM sont aujourd'hui dominants dans le domaine de l'informatique embarquée, en particulier la téléphonie mobile et les tablettes.

Ces processeurs sont fabriqués sous licence par un grand nombre de constructeurs.

Bien avant la Nintendo Switch de Nintendo, la puce ARM a même existé avant dans une cartouche Super Nintendo pour gérer (IA) l'intelligence artificielle du jeu Hayazashi Nidan Morita Shogi 2 sortie uniquement au Japon en 1995, le nom de la puce le ST018 fabriquer par Seta Corporation Société fondée en 1985 et qui a disparu en 2009, c'est une puce avec une fréquence de 21,47 MHz et le processeur est de type ARMv3 32 bits, (a voir liste des puces d'amélioration de la Super Nintendo dans la rubrique ST)

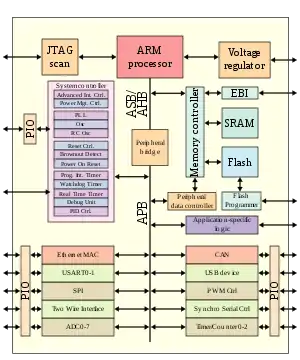

SoC ARM

Aujourd'hui, ARM est surtout connu pour ses systèmes sur une puce (SoC), intégrant sur une seule puce : microprocesseur, processeur graphique (GPU), DSP, FPU, SIMD, et contrôleur de périphériques. Ceux-ci sont présents dans la majorité des smartphones et tablettes. ARM propose des architectures qui sont vendues sous licence de propriété intellectuelle aux concepteurs. Ils proposent différentes options dans lesquelles les constructeurs peuvent prendre ce qui les intéresse pour compléter avec leurs options propres ou de concepteurs tiers. ARM propose ainsi pour les SoC les plus récents les microprocesseurs Cortex (Cortex-A pour les dispositifs portables de type smartphones et tablettes, Cortex-M pour le couplage à un microcontrôleur, Cortex-R pour les microprocesseurs temps réel), des processeurs graphiques (Mali), des bus AMBA sous licence libre, ainsi que les divers autres composants nécessaires à la composition du SoC complet. Certains constructeurs, tels que Nvidia, préfèrent produire leur propre processeur graphique, d'autres, comme Samsung, préfèrent prendre dans certains cas un processeur graphique de prestataire tiers ou d'ARM selon les modèles, et d'autres, comme Apple, modifient certains composants du microprocesseur en mélangeant plusieurs architectures processeur ARM (l'Apple A6 par exemple, mixe les technologies de microprocesseur Cortex-A9 et Cortex-A15).

Présentation des processeurs ARM

L'architecture ARM a initialement été développée en interne par la société britannique Acorn Computers, qui l'utilisa à partir de 1987 dans sa gamme d'ordinateurs 32 bits Archimedes.

ARM signifiait alors 'Acorn Risc Machine'. Ultérieurement la division « création de microprocesseurs » d'Acorn fut détachée de la société mère et devint la société « Advanced Risc Machine limited », se positionnant avec une offre indépendante pour le marché de l'électronique embarquée.

Une particularité des processeurs ARM est leur mode de vente. En effet, ARM Ltd. ne fabrique ni ne vend ses processeurs sous forme de circuits intégrés. La société vend les licences de ses processeurs de manière qu'ils soient gravés dans le silicium par d'autres fabricants. Aujourd'hui, la plupart des grands fondeurs de puces proposent de l'architecture ARM.

Le premier cœur produit est l'ARM2, vendu dans l'Archimedes A310 puis la gamme A4xx. Il comportait un pipeline à 3 étapes.

Le cœur le plus célèbre est l’ARM7TDMI qui comporte un pipeline à 3 étapes. De plus, le ARM7TDMI dispose d'un second jeu d'instructions appelé THUMB permettant le codage d'instructions sur 16 bits afin, ainsi, de réaliser une importante économie de mémoire, notamment pour les applications embarquées.

ARM Ltd. a ensuite développé le cœur ARM9 qui comporte un pipeline à 5 étapes. Cela permet ainsi l'augmentation du nombre d'opérations logiques sur chaque cycle d'horloge et donc une amélioration des performances en vitesse.

L'architecture ARM est utilisée dans de très nombreux domaines et équipe par exemple les calculatrices TI-Nspire et HP-50G. Cette architecture est également très répandue dans la téléphonie mobile.

De nombreux systèmes d'exploitation sont compatibles avec cette architecture :

- Symbian S60 avec les Nokia N97 ou Samsung Player HD,

- macOS (depuis le , concomitamment au lancement de la puce Apple M1), iOS, iPadOS, watchOS et tvOS avec les appareils Mac, iPhone, iPad, Apple Watch et Apple TV respectivement,

- Linux, avec la plupart des distributions ou avec Android,

- BlackBerry OS avec les BlackBerry,

- Windows CE, Windows Phone 7, Windows RT[2] et Windows 10,

- ReactOS,

- Risc OS, l'OS d'origine produit par Acorn,

- le système de la PlayStation Vita,

- le système de la Nintendo Switch,

- etc.

Il est également possible d’agglomérer des cœurs de différentes puissances, les plus faibles en consommation et puissance travaillant la majorité du temps, ceci permettant de minimiser la consommation électrique des cœurs plus puissants, lesquels sont activés uniquement en cas de forte demande de calcul afin d'en accélérer le traitement. Cette technologie est appelée big.LITTLE, elle est utilisée par Samsung, avec ses Exynos 5 octo (4 cortex-A7 faible consommation et 4 cortex-A15 de forte puissance), MediaTek et d'autres. Le Tegra 3 de NVidia, utilise une technique similaire avec un seul cœur de faible consommation et plusieurs de forte puissance.

Architecture et jeu d'instructions

L'architecture ARM est fortement inspirée des principes de conception RISC. Elle dispose de 16 registres généraux de 32 bits. Les instructions, codées sur 32 bits jusqu'à l'ARMv7 peuvent toutes disposer d'exécution conditionnelle ; sur l'architecture 64 bits (ARMv8[1]), quelques instructions seulement peuvent disposer d'exécution conditionnelle.

Le jeu d'instructions a reçu des extensions au fil du temps, telles que Thumb, permettant d'améliorer la densité du code, NEON, apportant des instructions SIMD, ou Jazelle, améliorant l'exécution de code Java.

Technologies des processeurs

Les processeurs qui suivent utilisent les technologies indiquées plus bas :

- MMU (memory management unit) : gestionnaire de mémoire permettant d'avoir une sécurité accrue (uniquement présente sur l'ARM710 et les ARM9). La MMU permet l'adressage virtuel de la mémoire, elle est nécessaire pour faire fonctionner certains systèmes d'exploitation comme Windows CE ou la plupart des Linux[3].

- MPU (en) (memory protection unit) : protection de la mémoire, faisant partie du MMU, donc protection simplifiée.

- DSP : composant électronique optimisé pour l'analyse numérique. Son application principale est le traitement du signal numérique (filtrage, encodage/décodage, extraction de signaux, etc.).

- FPU : unité de calcul sur les nombres flottants

Jazelle

Jazelle DBX (Direct Bytecode eXecution) est une technique permettant d'exécuter directement du bytecode Java dans les architectures ARM comme un troisième état d'exécution (et jeu d'exécution), en parallèle à l'ARM existant et au mode Thumb. Le support pour cet état est signalé par le « J » de l'architecture ARMv5TEJ et les noms de cœurs ARM9EJ-S et ARM7EJ-S. Le support de cet état est requis à partir d'ARMv6 (sauf pour le profil ARMv7-M). Malgré tout, les cœurs plus récents incluent seulement une implémentation triviale qui ne fournit pas d'accélération matérielle.

Thumb

Thumb est un jeu d'instructions 16 bits qui fournit un sous-ensemble des instructions ARM 32 bits classiques et permet un gain de mémoire important. Pour obtenir un codage plus compact de ces instructions, certains opérandes sont implicites et les possibilités offertes sont plus limitées.

Dans le mode Thumb, les instructions 16 bits offrent moins de possibilités. Seuls les branchements peuvent être conditionnels et plusieurs instructions sont limitées en accès à une partie réduite des registres généraux du processeur. Ces possibilités réduites améliorent la densité globale d'un programme, bien que certaines opérations nécessitent plus d'instructions. Cela peut réduire le temps de chargement du code en mémoire (libérant ainsi de la bande passante) et augmenter la probabilité de rester dans le cache d'instruction, augmentant ainsi considérablement les performances.

Du matériel embarqué tel que la Game Boy Advance a typiquement une petite quantité de RAM accessible via un bus de donnée 32 bits mais la majorité y est accédée via un second bus de 16 bits ou moins. Dans cette situation, il est très intéressant de compiler son programme en mode Thumb et d'optimiser à la main les quelques sections les plus consommatrices en utilisant le jeu d'instructions complet ARM 32 bits, permettant de placer ces instructions plus larges dans le bus d'accès mémoire 32 bits.

Le premier processeur contenant un décodeur d'instruction Thumb est l'ARM7TDMI. Toutes les ARM9 et supérieures (dont l'XScale) incluent un décodeur Thumb.

Thumb-2

La technologie Thumb-2 commence avec le cœur ARM1156 annoncé en 2003. Thumb-2 étend le jeu d'instructions limité 16 bits de Thumb par des instructions 32 bits additionnelles afin de donner plus de largesse au jeu d'instruction. Il en résulte un jeu d'instructions de largeur variable. Thumb-2 a pour visée d'atteindre une densité de code proche de Thumb tout en conservant des performances similaires au jeu d'instructions ARM en mémoire 32 bits.

Thumb-2 étend à la fois le jeu instructions Thumb et celui d'ARM avec notamment de la manipulation de champs de bits, des exécutions conditionnelles et des tables de branchement (en). Un nouveau langage assembleur unifié (unified assembly language, UAL) supporte simultanément la génération de code ARM et Thumb-2 depuis le même code source ; Les versions Thumb de code sur processeurs ARMv7 sont aussi capables que du code ARM, y compris pour écrire des fonctions de gestion d'interruption. Un peu d'attention est nécessaire et l'utilisation de la nouvelle instruction « IT » (if-then), qui permet d’exécuter quatre instructions successives en fonction d'une condition de test. En compilant en code ARM, cette instruction est ignorée, mais en compilant en Thumb-2, une réelle instruction est générée. Par exemple :

; if (r0 == r1)

CMP r0, r1

ITE EQ ; ARM : pas de code ... Thumb : instruction IT

; then r0 = r2;

MOVEQ r0, r2 ; ARM : conditionnel ; Thumb : condition via ITE 'T' (then)

; else r0 = r3;

MOVNE r0, r3 ; ARM : conditionnel ; Thumb: condition via ITE 'E' (else)

; Se rappeler que l'instruction MOV de Thumb n'a pas de bits pour encoder "EQ" ou "NE"

Toutes les puces ARMv7 supportent le jeu d'instructions Thumb-2. Les puces dans les séries Cortex-A, Cortex-R et ARM11 supportent les jeux d'instructions ARM et Thumb-2 (en mutuelle exclusion et selon l'état de l'indicateur interne T) tandis que les puces Cortex-M ne supportent pas le jeu d'instructions ARM[4],[5],[6].

Thumb Execution Environment (ThumbEE)

ThumbEE, également appelé Thumb-2EE, ou, commercialement Jazelle RCT pour (Runtime Compilation Target, signifiant en anglais « cible de compilation à la volée »), est annoncé en 2005 et apparait pour la première fois dans le processeur Cortex-A8. ThumbEE est le quatrième état de processeur, ajoutant de petits changements au jeu d'instructions étendu Thumb de Thumb-2. Ces changements rendent le jeu d'instructions particulièrement adapté à la génération de code au moment de l’exécution, par compilation à la volée, dans des environnements d’exécution contrôlés. ThumbEE est orienté vers les langages de programmation tels que Limbo, Java, C#, Perl, Python ou Ruby et permet aux compilateurs à la volée de générer moins de code de sortie sans affecter les performances.

Les nouvelles fonctionnalités de ThumbEE incluent la vérification automatique de pointeur nul à chaque instruction de chargement et sauvegarde, une instruction vérifiant les limites d'un tableau, un accès aux registres r8-r15 (où la Machine virtuelle Jazelle/DBX Java est maintenue), et des instructions spéciales qui appellent une fonction de rappel[7]. Les handlers sont des petites sections de code fréquemment appelées, utilisées généralement pour implémenter une fonctionnalité d'un langage de programmation de haut niveau tel que l'allocation de mémoire pour un nouvel objet. Ces changements ont été effectués pour réorienter une poignée d'opcodes et afin de savoir que le cœur est dans le mode ThumbEE.

Vector Floating Point (VFP)

La technologie VFP (vector floating point ou « virgule flottante vectorielle » en français) est une extension de coprocesseur de type FPU dans les architectures ARM. Il fournit le calcul des formats de virgule flottante simple précision à bas prix et de virgule flottante en double précision remplissant la norme ANSI/IEEE Std 754-1985 Standard for Binary Floating-Point Arithmetic. VFP fournit des calculs en virgule flottante permettant d'accomplir un vaste spectre d'applications et de besoins tels que les PDAs, les smartphones, la compression et décompression de voix, des graphiques en trois dimensions ou encore de l'audio numérique, des imprimantes, des boîtiers multimédias, et des applications automobiles. L'architecture VFP a eu pour but de supporter l’exécution de mode d'instructions vectorielles courtes mais elles opèrent séquentiellement sur chaque élément vectoriel et ainsi n'offre pas les performances d'un vrai parallélisme vectoriel comme le fait un SIMD. Ces modes vectoriels ont rapidement été retirés après leur introduction[8] pour être remplacés par la bien plus puissante unit NEON Advanced SIMD.

Quelques processeurs, tel que l'ARM Cortex-A8 ont été amputés avec un module VFPLite au lieu d'un module VFP complet, et requièrent environ dix fois plus de cycles d'horloge par opération en nombre flottant[9]. Les autres coprocesseurs à virgule flottante ou SIMD que l'on peut trouver dans les processeurs basés sur l'architecture ARM incluent NEON, les FPA, FPE, iwMMXt. Ils fournissent quelques fonctionnalités similaires aux VFP mais ne sont pas compatibles avec lui au niveau de l'opcode.

Il existe différentes version de VFP[10] :

- VFPv1, obsolète

- VFPv2, comportant 16 registres flottants 64 bits, supporte add, sub, neg, mul, div et sqrt

- VFPv3, selon les modèles, 16 ou 32 registres flottants 64 bits. VFPv3-F16 (Cortex A5 et A7) supporte le stockage des flottants demi-précision 16 bits.

- VFPv4, évolution de VFPv3 avec support de stockage demi-précision, 16 ou 32 registres 64 bits selon les modèles.

- VFPv5, utilisé dans les Cortex-M7 existe en version simple ou double précision

Advanced SIMD (NEON)

L'extension Advanced SIMD (également appelée NEON ou MPE pour Media Processing Engine (signifiant « moteur de calcul de médias » en anglais)) est un SIMD (Single Instruction, Multiple Data), combinant des jeux d'instruction 64 et 128 bits, qui fournissent de l'accélération de calcul standardisé pour les applications de médias, 2D/3D et de traitement du signal. NEON est inclus dans tous les cœurs Cortex-A8 mais est optionnel dans les cœurs Cortex-A9[11]. NEON peut faire du décodage MP3 sur un processeur fonctionnant à 10 MHz et peut encoder/décoder le codec audio GSM AMR à 13 MHz et permet d'accélérer le décodage de formats vidéo tels que h264 ou Real. Il contient un jeu d’instruction, un fichier de registres séparé et de l’exécution matérielle indépendante[12]. Il comporte 32 registres 64 bits flottants, qu'il partage avec le FPU, pouvant être couplés pour former 16 registres de 128 bits flottants, et accepte aussi que ces registres soient traités comme des entiers signés ou non signés de 8, 16, 32 et 64 bits. Ce SIMD supporte jusqu'à 16 opérations simultanées. Des cœurs comme le ARM Cortex-A8 et le Cortex-A9 supportent des vecteurs 128 bits mais ne traitent que 64 bits à la fois[9], tandis qu'à partir du plus récent Cortex-A15, il peut traiter 128 bits à la fois.

LPAE

La technologie LPAE (Large Physical Address Extension)[13] a été implémentée pour la première fois dans les Cortex A de 3e génération (Cortex-A7, Cortex-A15 et Cortex-A17). Cette extension est utilisée sur les processeurs 32 bits d'ARM, permettant d'étendre l'adressage de 32 bits (4 gigaoctets maximum) à 40 bits (1 téraoctet maximum). Elle nécessite un MMU comportant l'extension VMSAv7. Avec cette extension, la granularité du contrôle du MMU est de 4 Kio.

Cette extension fonctionne en plusieurs étapes :

- Elle traduit d'abord une adresse virtuelle (VA) 32 bits dans une adresse physique intermédiaire (IPA) 40 bits ;

- Elle traduit l'IPA en adresse physique (PA) 50 bits.

Le registre ID_MMFR3 fournit la taille de l'adresse physique supportée (32 bits, 36 bits ou 40 bits).

TrustZone

TrustZone est une technologie de chiffrement et sécurisation des échanges avec des plates-formes tierces, selon les normes Trusted execution environment (en) (TEE, l’équivalent sur mobile du module de plateforme fiable sur ordinateur[14]). Le but est d'empêcher l'utilisateur ou des applications tierces installées sur le terminal d'accéder aux données échangées dans cet environnement dit de confiance. Elle est, par exemple, utilisée dans les environnements de fichiers protégés par la gestion numérique des droits (GND), également appelé DRM en anglais.

Processeurs graphiques ARM

ARM propose également des processeurs graphiques (GPU) appelés Mali qui peuvent être intégrés aux architectures des SoC ARM. La première série, Mali 200, utilisée dans des processeurs tels que le SoC Telechips TCC890x[15].

La seconde série, Mali 300 ne semble pas avoir été utilisée par les constructeurs.

La troisième série, Mali 400 MP est proposée sur des processeurs plus haut de gamme, généralement, Cortex A9, comme le ST-Ericsson U8500[16], les Samsung Exynos 4 ou l'Amlogic 8726-M, mais aussi sur les Cortex A8 AllWinner A1X.

La série Mali 600 est à destination des Cortex A15. Elle équipe notamment la série de Samsung Exynos 5. Le premier modèle a été le Mali T604[17].

L'API générique d'accès au GPU MALI compatible EXA/DRI2 libres à sources ouvertes (licences Apache et MIT) est disponible pour les Mali 200, 300, 400 et 600 sur la plateforme Linux[18], mais la partie la plus basse d'accès au processeur, dépendant du constructeur reste fermée.

Le projet Lima driver a été créé pour développer un pilote libre permettant d'utiliser pleinement ces processeurs. En , il dépasse déjà les performances des pilotes propriétaires sur les séries Mali 400[19].

De nombreux SoC ARM comportent cependant un GPU PowerVR ou plus rarement d'autres processeurs graphiques (Qualcomm Adreno, Vivante, Nvidia), qui possèdent tous des pilotes pour Linux, mais dont la partie 3d est propriétaire et à sources fermées. Le projet Freedreno a les mêmes visées pour les Adreno que le projet Lima driver pour la série des Mali.

Architectures

| Architecture | Famille(s) |

|---|---|

| ARMv1 | ARM1 |

| ARMv2 | ARM2, ARM3 |

| ARMv3 | ARM6, ARM7 |

| ARMv4 | StrongARM, ARM7TDMI, ARM8, ARM9TDMI |

| ARMv5 | ARM7EJ, ARM9E, ARM10E, XScale, FA626TE, Feroceon, PJ1/Mohawk |

| ARMv6 | ARM11 (en) |

| ARMv6-M | ARM Cortex-M (ARM Cortex-M0, ARM Cortex-M0+, ARM Cortex-M1) |

| ARMv7-A | ARM Cortex-A (Gen1 : ARM Cortex-A8, Gen2 : ARM Cortex-A9 MPCore, ARM Cortex-A5 MPCore, Gen3 : ARM Cortex-A7 MPCore, ARM Cortex-A12 MPCore, ARM Cortex-A15 MPCore, Adaptation tierce : Scorpion, Krait, PJ4/Sheeva, Swift |

| ARMv7-M | ARM Cortex-M (ARM Cortex-M3, ARM Cortex-M4, ARM Cortex-M7) |

| ARMv7-R | ARM Cortex-R (ARM Cortex-R4, ARM Cortex-R5, ARM Cortex-R7) |

| ARMv8-A | ARM Cortex-A35, ARM Cortex-A50 (ARM Cortex-A53, ARM Cortex-A57), ARM Cortex-A72, ARM Cortex-A73, X-Gene, Denver, Cyclone, Exynos M1/M2 |

| ARMv8.2-A | ARM Cortex-A55, ARM Cortex-A65, ARM Cortex-A75, ARM Cortex-A76 |

| ARMv8.3-A | ARM Cortex-A65AE (seulement LDAPR, le reste en 8.2), ARM Cortex-A76AE (idem A65AE) |

| ARMv8-M | ARM Cortex-M23, ARM Cortex-M33 |

| ARMv8-R | ARM Cortex-R53 |

Divers processeurs ARM

- ARM1 (1985) : premier prototype de cœur ARM

- Famille ARM2 (1987) : premier ARM commercialisé dans l'Archimedes d'Acorn : Pipeline 3 niveaux, adressage sur 24 bits alignés (16 registres de 32 bits soit 64 Mio adressables), 8 MHz puis 12 MHz

- Famille ARM3 : Interface FPU, fréquence 25 puis 33 MHz, 4K cache

- Famille ARM4

- Famille ARM4T

- Famille ARM5TE (2000) : arrivée de Thumb et de fonctionnalités de DSP

- Famille ARM5TEJ (2000) : arrivée de Jazelle

- Famille ARM6 sorti en 1990

- Famille ARM7 :

- ARM720T (MMU)

- ARM7TDMI

- ARM7TDMI-S

- ARM7EJ-S : DSP et Jazelle

- Famille ARM9 (5 niveaux de pipeline sur les entiers, MMU) : ARM920T (double cache de 16 ko) et ARM922T (double cache de 8 ko)

- Famille ARM9E

- ARM946E-S : DSP, double cache, MPU, 1 port AHB

- ARM926EJ-S: DSP, double cache, MMU, 2 ports AHB

- ARM966E-S : DSP, double cache, MPU, 1 ports AHB

- Famille ARM10E

- ARM1020E : DSP, double cache de 32 ko, MMU

- ARM1022E : identique au ARM1020E, sauf le double cache de 16 ko

- ARM1026EJ-S

- Famille ARM11 : SIMD, Jazelle, DSP, Thumb-2

- ARM1136JF-S : FPU

- ARM1156T2-S

- ARM1156T2F-S : FPU

- ARM1176JZ-S

- ARM1176JZF-S : FPU

- Famille Cortex-A, processeur applicatif: Architecture ARMv7-A, SIMD, Jazelle, DSP, Thumb-2

- Cortex-A5

- Cortex-A5 MPCore : Cortex-A5 version multiprocesseur (1 à 4 CPU)

- Cortex-A7 MPCore : Cortex-A7 multiprocesseur (1 à 8 CPU, LITTLE)

- Cortex-A8

- Cortex-A9

- Cortex-A9 MPCore : Cortex-A9 version multiprocesseur (1 à 4 CPU), 45, 32[20] et 28 nm jusqu’à 2 GHz (3,1 GHz dans certaines conditions [21])

- Cortex-A12 MPCore, jamais produit, finalement remplacé par le Cortex-A17 (big)

- Cortex-A15 MPCore : Cortex-A15 multiprocesseur (1 à 4 CPU), 45, 32 et 28 nm (big)[22] (20 nm projeté), jusqu’à 2,5 GHz

- Cortex-A17 MPCore (big)

- Famille Cortex-R, processeur temps-réel: Architecture ARMv7-R et ARMv8-R

- Cortex-R4

- Cortex-R52

- Famille Cortex-M, processeur embarqué : Architecture ARMv6-M, ARMv7-M et ARMv8-M

- Cortex-M0

- Cortex-M0+

- Cortex-M1

- Cortex-M3

- Cortex-M4

- Cortex-M7

- Cortex-M23

- Cortex-M33

- Famille ARMv7, (processeurs 32 bits)

- Cortex-A32

- Famille ARMv8, (processeurs 64 bits)

- Cortex-A35 (LITTLE)

- Cortex-A53 (LITTLE)

- Cortex-A57 (big)

- Cortex-A72 (big)

- Cortex-A73 (big)

- Famille ARMv8.2, (processeurs 64 bits)

- Cortex-A55 (LITTLE)

- Cortex-A75 (big)

- Cortex-A76 (big)

Fabricants de processeurs ARM

La propriété intellectuelle appartient à une société britannique, mais les processeurs fabriqués sous licence le sont par différentes entreprises de par le monde. Parmi les entreprises fabriquant les modèles des séries Cortex (les plus avancées), la majorité se trouve en Asie (20), suivie par les États-Unis (13) et enfin par l'Europe (6).

- Accent

Italie

Italie - Applied Micro Circuits Corporation

États-Unis ARMv8[23]

États-Unis ARMv8[23] - Alchip

Taïwan

Taïwan - AllWinner Technology (ou Quanzhi)

Chine (Cortex A8 et A7 avec Mali 400MP et VPU CedarX maison décodant le QuadHD 2160P[24])

Chine (Cortex A8 et A7 avec Mali 400MP et VPU CedarX maison décodant le QuadHD 2160P[24]) - Altera

États-Unis (FPGA Cortex-A9 MPCore)

États-Unis (FPGA Cortex-A9 MPCore) - Amlogic www.amlogic.com

États-Unis/

États-Unis/ Chine (Cortex A9)

Chine (Cortex A9) - Anyka

Chine

Chine - Apple

États-Unis

États-Unis - Atmel

États-Unis

États-Unis - Broadcom

États-Unis (Cortex A9)

États-Unis (Cortex A9) - Celestial Semiconductor

Chine

Chine - Cypress Semiconductor

États-Unis

États-Unis - Freescale

États-Unis

États-Unis - Fujitsu

Japon (cortex M3, Cortex A9, A7, A15[25])

Japon (cortex M3, Cortex A9, A7, A15[25]) - HiSilicon

Chine (Cortex A9, A7, A15[26],[27])

Chine (Cortex A9, A7, A15[26],[27]) - Holtek

Taïwan (Cortex M0+, Cortex M3)

Taïwan (Cortex M0+, Cortex M3) - Huawei Technologies

Chine (Cortex A9, A7, A15)[28]

Chine (Cortex A9, A7, A15)[28] - Infineon

Allemagne

Allemagne - Inside Secure

France

France - LG Electronics (Cortex-A50)

Corée du Sud[29]

Corée du Sud[29] - Matsushita

Japon (Cortex A8[30])

Japon (Cortex A8[30]) - Marvell

États-Unis

États-Unis - MediaTek

Taïwan (Cortex A9[31], A7, A15)

Taïwan (Cortex A9[31], A7, A15) - NXP Semiconductors

Pays-Bas

Pays-Bas - Nufront (conception)

Chine, usiné par TSMC

Chine, usiné par TSMC  Taïwan (Cortex A9)

Taïwan (Cortex A9) - Nvidia

États-Unis (Cortex A9, Cortex A15 (Tegra K1), Cortex A53/A57 (Tegra X1))

États-Unis (Cortex A9, Cortex A15 (Tegra K1), Cortex A53/A57 (Tegra X1)) - Parrot

France (ARM926ejs (P6), Cortex A9 (P7))

France (ARM926ejs (P6), Cortex A9 (P7)) - Qualcomm

États-Unis

États-Unis - Renesas

Japon (Cortex A9[32])

Japon (Cortex A9[32]) - Phytium Technology (

Chine, Phytium Mars)

Chine, Phytium Mars) - Rockchip

Chine (Cortex A8, Cortex A9 MPcore, Mali 400 MP[33])

Chine (Cortex A8, Cortex A9 MPcore, Mali 400 MP[33]) - Samsung

Corée du Sud (Cortex A8, Cortex A9, A15 (Exynos 5250)[34], A7)

Corée du Sud (Cortex A8, Cortex A9, A15 (Exynos 5250)[34], A7) - Silicon Labs

États-Unis (Cortex M0+, M3, M4)

États-Unis (Cortex M0+, M3, M4) - Spreadtrum (

Chine)

Chine) - STMicroelectronics

France

France  Italie et ST-Ericsson (Cortex A9 (U9500), Cortex A15 (A9600)[35]), SoC comportant Cortex-M4F + DSP (STM32)

Italie et ST-Ericsson (Cortex A9 (U9500), Cortex A15 (A9600)[35]), SoC comportant Cortex-M4F + DSP (STM32) - Telechips

Corée du Sud

Corée du Sud - Texas Instruments

États-Unis (Cortex A8 (OMAP3), Cortex A9 (OMAP4), Cortex A15 (OMAP5))

États-Unis (Cortex A8 (OMAP3), Cortex A9 (OMAP4), Cortex A15 (OMAP5)) - Toshiba

Japon

Japon - VIA

Taïwan

Taïwan - Xilinx

États-Unis Zynq (FPGA Cortex-A9 MPCore).

États-Unis Zynq (FPGA Cortex-A9 MPCore). - ZiiLABS

Singapour

Singapour - ZTE

Chine

Chine

Notes et références

- 1 2 ARMv8 : le 64 bits va arriver (28 octobre 2011).

- ↑ Quoi de neuf dans Windows 8 ?, Cachem.fr, publié le 23 mai 2011.

- ↑ uclinux excepté, mais pas seulement:(en)site officiel

- ↑ (en) « ARM Processor Instruction Set Architecture », Arm.com (consulté le )

- ↑ (en) « ARM aims son of Thumb at uCs, ASSPs, SoCs »(Archive.org • Wikiwix • Archive.is • Google • Que faire ?), Linuxdevices.com (consulté le )

- ↑ (en) « ARM Information Center », Infocenter.arm.com (consulté le )

- ↑ (en) Arm strengthens Java compilers: New 16-Bit Thumb-2EE Instructions Conserve System Memory by Tom R. Halfhill 2005.

- ↑ « VFP directives and vector notation », Arm.com (consulté le )

- 1 2 « Differences between ARM Cortex-A8 and Cortex-A9 », Shervin Emami (consulté le )

- ↑ (en) Phillip Johnston, « Demystifying ARM Floating Point Compiler Options »,

- ↑ « Cortex-A9 Processor », Arm.com (consulté le )

- ↑ « About the Cortex-A9 NEON MPE », Arm.com (consulté le )

- ↑ (en) « Principles of ARM® Memory Maps — White Paper — 2.1.2 32-bit ARMv7 with LPAE », ARM (consulté le )

- ↑ (en-US) Anasia D'mello, « TPM and TEE are partnering not competing, GlobalPlatform boss reports », sur IoT Now, (consulté le ).

- ↑ (en) TCC8900 development board

- ↑ (en) MOP500 development board

- ↑ (en) Mali-T604 sur ARM

- ↑ (en) Open Source Mali GPUs Linux EXA/DRI2 And X11 Display Drivers sur malideveloper.com

- ↑ (en) The lima mesa driver runs es2gears

- ↑ Exynos 4 Quad sur samsung.com

- ↑ (en)TSMC's 28 nm Based ARM Cortex-A9 Test Chip Reaches Beyond 3 GHz sur TSMC.com

- ↑

- ↑ (en) Applied Micro X-Gene 64-Bit ARMv8 Server-on-Chip Presentation

- ↑ (zh) A1X by Allwinner Technology Co., Ltd 珠海全志科技股份有限公司 sur ARM.com

- ↑ (ja) ARMコアマクロ sur jp.Fujitsu.com

- ↑ (zh) 海思半导体获ARM技术授权,用于创新的3G/4G基站网络基础架构及移动计算应用 sur arm.com

- ↑ (en)HiSilicon Announces K3V2 Quad-core Application Processor

- ↑ sur ses propres smartphones.

- ↑ (en) (ja) (zh-CN) LG Electronics Becomes Lead Partner For ARM Cortex-A50 Family Of Products And Next-Generation Mali GPUs sur ARM.com

- ↑ (en) Processor licensees

- ↑ (en) MediaTek Launches MT6575 Android Platform sur MediaTek.com

- ↑ (en) Renesas Mobile Introduces First Integrated LTE Triple-Mode Platform Optimised for Full-Featured, High Volume Smartphones

- ↑ (en) (zh) Rockchip Licenses a Wide Range of ARM IP for Turnkey Solution Targeting Mass Market, Cost-Effective Android Tablets sur ARM.com

- ↑ (en)Samsung Announces Industry First ARM Cortex-A15 Processor Samples for Tablet Computers sur Samsung.com, le 30 novembre 2011

- ↑ (en) « ARM Cortex-A15 processor adopts Imagination's new graphics IP » [archive du ] sur Linuxfordevices.com

Articles connexes

- Le processeur StrongARM pour les applications embarquées demandant de la puissance de calcul.

- Le processeur Intel (revendu à Marvell) XScale qui est dérivé de l'architecture ARM.

- RISC-V